# CHIP DESIGN COMPETITION SPECIFICATIONS 2024

| CHANGE TRACKING TABLE |            |                        |                                                                                 |  |  |  |  |  |

|-----------------------|------------|------------------------|---------------------------------------------------------------------------------|--|--|--|--|--|

| Version               | Date       | Change Place           | Description                                                                     |  |  |  |  |  |

| 1.0                   | 07.12.2024 | 2024 First Publication |                                                                                 |  |  |  |  |  |

| 1.1                   | 20.02.2024 |                        | Update of the application deadline<br>under the Competition Schedule<br>heading |  |  |  |  |  |

| 1.2                   | 26.02.2024 |                        | Add "APP-4 Microcontroller<br>Peripheral Registers"                             |  |  |  |  |  |

| 1.3                   | 27.03.2024 |                        | Add USB FS Device and JTAG peripheral information at "APP-4"                    |  |  |  |  |  |

| 1.4                   | 03.04.2024 |                        | Update under the Competition<br>Schedule heading                                |  |  |  |  |  |

| 1.5                   | 15.04.2024 |                        | Update under the Competition<br>Schedule heading                                |  |  |  |  |  |

# **TABLE OF CONTENTS**

| FIGURE AND TABLE LIST                                                               | 4  |

|-------------------------------------------------------------------------------------|----|

| ABBREVIATIONS                                                                       | 5  |

| 1 PURPOSE                                                                           | 7  |

| 2 COMPETITION SCHEDULE                                                              | 7  |

| 3 GENERAL INFORMATION ABOUT THE COMPETITION                                         | 7  |

| 3.1 Participation Rules                                                             |    |

| 3.2 Reports and Presentation                                                        | 9  |

| 3.2.1 Preliminary Design Report (PDR)                                               | 9  |

| 3.2.2 Detailed Design Report (DDR)                                                  | 10 |

| 3.2.3 Final Evaluation Presentation and Design Outputs                              | 10 |

| 3.3 Evaluation                                                                      | 10 |

| 3.3.1 Digital Processor Design Category                                             | 11 |

| 3.3.2 Analog Design Category                                                        |    |

| 3.3.3 Microcontroller Design Category                                               | 12 |

| 3.4 Contact                                                                         |    |

| 4 TECHNICAL RULES                                                                   | 13 |

| 4.1 Design Environment and Technology                                               |    |

| 4.2 Design Requirements                                                             |    |

| 4.2.1 Digital Processor Design Category                                             |    |

| 4.2.2 Analog Design Category                                                        |    |

| 4.2.3 Microcontroller Design Category                                               |    |

| 4.3 Design Outputs                                                                  | 19 |

| 5 AWARD                                                                             | 21 |

| 5.1 Minimum Success Criteria for Award Ranking in Digital Processor Design Category |    |

| 5.2 Minimum Success Criteria for Award Ranking in Analog Design Category            |    |

| 5.3 Minimum Success Criteria for Award Ranking in Microcontroller Design Category   |    |

| 6 GENERAL RULES                                                                     | 23 |

| 7 CODES OF CONDUCT<br>Responsibility Statement                                      | 23 |

|                                                                                     |    |

| 8 APPENDIX                                                                          | 24 |

| APP-1 Instructions to Be Supported                                                  |    |

| APP-2Peripheral Details                                                             |    |

| APP-3Verilog RTL Writing Rules                                                      |    |

| APP-4 Microcontroller Peripheral Registers                                          | 31 |

# FIGURE AND TABLE LIST

| Figure 1: Battery Discharge Graph                                   | 15          |

|---------------------------------------------------------------------|-------------|

| Figure 2: Block Diagram of Bandgap Reference, LDO Voltage Regulator | and Voltage |

| Controlled Oscillator Circuits                                      | 16          |

| Table 1: Competition Schedule                      | 7  |

|----------------------------------------------------|----|

| Table 2: Digital Processor Category Awards         |    |

| Table 3: Analog Category Awards                    | 21 |

| Table 4: Microcontroller Category Awards           | 22 |

| Table 5 : RV32I Basic Instruction Set              | 24 |

| Table 6: RV32M Standard Instruction Set Extensions | 24 |

| Table 7: RV32A Standard Instruction Set Extensions | 25 |

| Table 8: RV32F Standard Instruction Set Extensions | 25 |

| Table 9: RV32B Standard Instruction Set Extensions | 25 |

| Table 10: UART Memory Map                          | 27 |

| Table 11: UART Control Register                    |    |

| Table 12: Example of baud rate calculation values  | 28 |

| Table 13: UART Status Register                     |    |

| Table 14: UART Data Read Register                  | 29 |

| Table 15: UART Write Data Register                 |    |

|                                                    |    |

# **ABBREVIATIONS**

ADC: Analog-to-Digital Converter ALU: Arithmetic Logic Unit BILGEM: Informatics and Information Security Research Center BP: Band Pass **CNN:** Convolutional Neural Network **DC:** Direct Current **DCT:** Direct Cosine Transform **DDK:** Advisory and Evaluation Board **DEF:** Design Exchange Format **DRC:** Design Rule Check **DRV:** Design Rule Violation **DSP:** Digital Signal Processing **DDR:** Detailed Design Report **EDA**: Electronic Design Automation FPGA: Field Programmable Gate Array **GDS:** Graphic Data System **GPS:** Global Positioning System HDL: Hardware Description Language **IIP3:** Input Third Order Intercept Point **IPC:** Instruction per Cycle **IRN:** Input Referred Noise **ISA:** Instruction Set Architecture **IP:** Intellectual Property **KYS:** Enterprise Management System LDO: Low Drop-out LTE: Long Term Evolution LVS: Layout versus Schematic MCU: Microcontroller Unit MPW: Multi Project Wafer PDK: Process Design Kit **PDR:** Preliminary Design Report **PSRR:** Power Supply Rejection Ratio **QVGA**: Quarter Video Graphics Array **RISC:** Reduced Instruction Set Architecture **RF:** Radio Frequency **RTL:** Register Transfer Level **SDF:** Standard Delay Format SoC: System-on-Chip **SV:** SystemVerilog T3 Foundation: Turkiye Technology Team Foundation TT: Typical-Typical TÜBİTAK: Scientific and Technological Research Council of Turkiye **UART:** Universal Asynchronous Receiver Transmitter

USB: Universal Serial Bus UVM: Universal Verification Methodology VCO: Voltage Controlled Oscillator WIPO: World Intellectual Property Organization

# **1 PURPOSE**

The Chip (Integrated Circuit) Design Competition, which was opened to university students for the first time in 2022 within the scope of TEKNOFEST, aims to raise awareness in the field of microelectronic technologies in associate, undergraduate and graduate (master) students and to provide students with knowledge on IC design. The competition is also organized to encourage teamwork and to lead the formation of competent human resources in this field by developing micro-electronic technologies with practical applications.

This document has been created to define all the rules and requirements of the Chip Design Competition, which is organized by the TÜBİTAK BİLGEM Integrated Design and Education Laboratory (TÜTEL) and Yongatek Microelectronics within the scope of TEKNOFEST Aviation, Space and Technology Festival (TEKNOFEST) Technology Competitions. The analog and digital processor design categories are organized by **TUTEL**, the microcontroller design category is organized by **Yongatek Microelectronics**.

# **2 COMPETITION SCHEDULE**

Table 1: Competition Schedule

| DESCRIPTION                                                                | DATE               |

|----------------------------------------------------------------------------|--------------------|

| Application Deadline for the Competition                                   | 29.02.2024         |

| Submission Deadline for Preliminary Design Report (PDR)                    | 15.03.2024 17:00   |

| Announcement of the Teams Passing the<br>Preselection based on PDR Results | 22.03.2024         |

| QA Session                                                                 | 22.04.2024         |

| Submission Deadline for Detail Design Report (DDR)                         | 30.06.2024 17.00   |

| Announcement of Finalist Teams                                             | 15.07.2024         |

| QA Session                                                                 | 22.07.2024         |

| Deadline for Finalizing the Design                                         | Not yet determined |

| Final Presentations and Demos                                              | Not yet determined |

# **3 GENERAL INFORMATION ABOUT THE COMPETITION**

The competition consists of three categories; analog, digital processor, and microcontroller. For the competitions organized by TÜTEL, it is expected that a customized processor with RISC-V Instruction Set Architecture (ISA) will be designed in the digital processor design category. Designing a bandgap reference circuit, a LDO voltage controller, and a Voltage Controlled Oscillator (VCO) is expected in the analog design category. In the microcontroller design category organized by Yongatek Mikroelektronik, it is expected to design and verify a microcontroller with various interface elements and memory units using a ready-made processor core.

What is expected from the teams that will participate in the competition is to prepare the preliminary design report, detailed design report, complete the design, prepare the design outputs and make a presentation/demo in the final for the hardware that meets the design criteria specified in this document.

Applications will be made through the official website of TEKNOFEST Technology Competitions (<u>www.teknofest.org</u>) until February 29, 2024.

## **3.1 Participation Rules**

- Higher education (associate, undergraduate and master) students studying in Turkiye and abroad can participate in the competition.

- Participation in the competition can be made individually or as a team. Teams must consist of a maximum of 5 people (excluding consultant).

- Number of graduate students (master) in the teams cannot exceed 2.

- A competitor can take part in teams in different categories, but not in different teams in the same category.

- Teams can only have 1 person as a consultant. It is not required to have a consultant. A consultant can advise only one team per category.

- Along with the competition application, by using KYS system, approved student documents must be submitted for students, and a certified document showing that they are a lecturer/staff or research assistant must be submitted for advisors.

- Teams can be formed from a single school or as a mixed team with one or more higher education students coming together.

- Each team participating in the competition can submit only one design.

- Competitors who have completed the team formation process must apply to the competition in accordance with their project.

- Between the application dates, the team captain/advisor registers through the system, makes the correct and complete registration of the consultant and/or team captain/team members, if any, and sends an invitation to the advisor and members' e-mails, if any. The member to whom the invitation is sent, logs in to the Application system, accepts the invitation from the "My Team Information" section and the registration is completed. Otherwise, the registration will not be completed.

- All necessary processes within the scope of the competition (Application, Report Submission, Announcement of the Report Results, Financial Support Application, Objection, Member Addition/Removal, etc.) are done through the KYS system. Teams are required to follow their processes through the KYS system.

- Adding/removing members can be done until the Detail Design Report Submission date.

- During the competition process, the processes of applying through the KYS, uploading reports and filling out forms are under the authority of the team captain and/or the consultant, and the competition processes are managed through these people.

- Transportation and accommodation support to be provided to the finalist teams is limited. The number of people to be supported is 3 people (including the consultant) per team and TEKNOFEST Competitions Committee has the right to make changes.

- TEKNOFEST Competitions Committee has the authority to limit the number of members in the festival area. In case of restrictions, the committee will inform.

- Throughout the competition process, education level at the time of application will be considered.

- Applications of TÜTEL and Yongatek Microelektronics employees will not be evaluated.

## **3.2 Reports and Presentation**

- The format in the GENERAL RULES section should be followed for references from previous year reports. Other than that, IEEE format should be followed for references from other sources.

- Two reports, a preliminary design report and a detail design report, will be submitted. The technical information required in the relevant headings of the reports should be conveyed in detail.

- Report templates are published on the <u>competition website</u>.

- Reports can be prepared in Turkish or English. It is mandatory to use a single language in a report.

- The reports are uploaded to the application system in PDF format with a maximum size of 60 MB until 05.00 pm in the specified deadlines. Otherwise, the team will be eliminated from the competition.

- The reports should be prepared in A4 format, 11 point, Calibri font, with a line spacing of 1.15 and 2.5 cm at the bottom, top and sides. The preliminary design report should have a maximum of 9 pages, and the detailed design report should have a maximum of 30 pages (including the cover page, pictures, tables, references).

- The report is evaluated within the scope of scientific and technical criteria specified by DDK members who are experts in their fields. Teams with a score below what is determined by DDK are eliminated from the race.

- Teams with successful reports are announced on the <u>www.teknofest.org</u> page.

- In case of an ethical violation such as plagiarism, copying etc., the report will not be evaluated and the corresponding team will be eliminated from the competition. This rule is applied for the application of the same university/club/society etc. regardless of category/race.

# **3.2.1 Preliminary Design Report (PDR)**

Preliminary design report is expected to include the following sections:

Block diagram of the overall design, target performance summary table, system level importance of targeted performance measures, schematics of the possible critical circuit core, verification plan and methods, brief description of the circuit and design

techniques to be used, applicable references (e.g., an article that inspires your design, all the open-source blocks you'll reuse, etc.). The design structure given in the PDR can be changed later, provided that change reasons are explained.

The up-to-date report template will be shared on the <u>competition website</u>.

In order to proceed to the next stage within the scope of this competition, the preliminary design report must be submitted and deemed successful.

# **3.2.2 Detailed Design Report (DDR)**

In the detailed design report of the digital processor design category, the details of the design, how the problems presented in the specification were handled, block diagrams, simulation and IC flow results should be included.

In the analog design category detailed design report, it is expected that the schematic level design will be completed and reported with the results.

Microcontroller Unit (MCU) category detailed design report should include topics such as how the requirements presented in the specification are realized, block diagrams, simulation and synthesis results. The processor core in the MCU and the "Spike" RISC-V instruction set simulation tool must be verified by comparing the results of the programs provided by DDK. In addition, it is expected that the test results and coverage report of the UART peripheral unit that is requested to be verified with SV/UVM will be detailed. While SV/UVM verification must be shown to be working correctly for other peripherals, SV/UVM verification is not required, only SV/UVM is required for UART.

The up-to-date report template will be shared on the competition website.

Teams that have passed to the DDR stage are obliged to submit their reports on the date specified in Table 1.

According to the DDR results, the teams that will participate in the final evaluation will be announced on the date specified in Table 1.

# **3.2.3 Final Evaluation Presentation and Design Outputs**

Final evaluation presentation and design outputs (schematic, RTL, GDSII etc.) must be submitted by the date specified as "Deadline for Finalizing the Design" in Table 1. Changes made to GitHub repositories after 11.59 pm on the relevant date will not be taken into consideration. The presentations should be uploaded on the same date until 05.00 pm. Presentations in the competition area will be made through presentation files uploaded to the system. Using the design outputs, the results in the presentation will be verified and the non-conforming groups will be eliminated. For this reason, the design outputs must be up-to-date and compatible with the presentation. Details of the design outputs are given in Design Outputs section.

# 3.3 Evaluation

Teams that pass the PDR stage will be entitled to participate in the DDR stage. PDR and DDR reports will be evaluated in accordance with the template to be announced

on the <u>competition website</u>. Teams that pass the DDR stage will be eligible to participate in the presentation and demo evaluation. Presentation evaluation will be made by the competition jury according to the oral presentation and the answers to the questions of the evaluators. Teams that are not in the competition area although they are entitled to participate in the presentation evaluation are considered as withdrawn from the competition. First, second and third competitors will be determined according to the weighted points of all stages.

## **3.3.1 Digital Processor Design Category**

Evaluation consists of several stages. Firstly, the processor (RV32IMAFB\_Zicsr (only the machine mode) instruction set processor, UART peripheral) requested from the competitors will be put into a test environment, and the interface of the processor should be compatible with the wrapper module that will be shared with the competitors. Test codes will be loaded into the main memory located in the top module wrapper. In this test environment, it will be tested whether or not the competitor implements the instruction set correctly. During the tests, some boundary conditions (such as dividing a number by zero) will also be tested. For testing the UART block, commands will be sent to this block over the peripheral bus in accordance with the register address space given in APP-3. Secondly, this block will be tested with the processor first in the simulation environment, then on the FPGA.

Projects that have been tested and found to meet minimum requirements will be subjected to performance analysis. In this analysis, various performance tests (e.g., CoreMark) will be run on the processor. IC flow, design evaluation, and verification work will be carried out on the designs after presentations and demos. The total score that can be obtained at the end of the competition will be a maximum of 100 points and the calculation will be made as follows.

## Total Points = (0.1 \* PDR Points) + (0.2 \* DDR Points) + (0.2 \* Presentation Points) + (0.1 \* Demo Points) + (0.25 \* IC Flow Points) + (0.15 \* Design and Verification Points)

Expectations and criteria in scoring will be shared later. Those who have not updated their GitHub repo in at least one of the 20-day intervals following the later-announced release date will lose points from the Design and Verification evaluation. In case of a tie, the team with the most Chip Flow plus Design and Verification points will advance in the ranking.

## **3.3.2 Analog Design Category**

Scoring will be made out of 100 points and reports, presentations, and demos will constitute the entire score. Reports are 40% of the total score and the remaining 60% will be presentation and performance criteria. Evaluation will be made through post-layout simulations in the analog design category.

The total score that can be obtained at the end of the competition will be a maximum of 100 points and the calculation will be made as follows.

## Total Score = (0.15 \* PDR Points) + (0.25 \* DDR Points) + (0.40 \* Presentation Points) + (0.20 \* Performance Criteria Points)

Performance Criteria Points will be determined by considering the performances, area and power consumptions of the bandgap reference voltage circuit, LDO voltage regulator circuit and voltage controlled oscillator (VCO) circuit.

# **3.3.3 Microcontroller Design Category**

The module, which will be designed within the scope of the microcontroller design category, will consist of two separate parts: FPGA and physical design realization. The competitors will first create a design on an FPGA development board that will fulfill the tasks given in the Microcontroller section of the Microcontroller Design Category under the title of Design Requirements and run this design in real-time on the FPGA card. In the next stage, they will create GDSII outputs in the form to be sent to production with the IC design software that will be provided for physical design. Detailed information about the IC physical design will be clarified in the future.

Technical information about what needs to be done for the FPGA and Physical Design stages is defined in the Microcontroller Design Category heading under the TECHNICAL RULES heading.

The total score that can be obtained at the end of the competition will be a maximum of 100 points and the calculation will be made as follows.

Total Points = (0.1 \* PDR Points) + (0.2 \* DDR Points) + (0.2 \* Presentation Points) + (0.1 \* Demo Points) + (0.25 \* IC Flow Points) + (0.15 \* Verification Points)

# **3.4 Contact**

For technical questions about the contest, communication will be made through the messaging group to be determined later. It is the responsibility of the competing team to actively follow this group and to follow the announcements and questions & answers in this group. Referees and jury committees are not responsible for the failure of the teams to reach up-to-date information as a result of not following the specified e-mail group.

Questions about the organizational parts of the competition should be submitted via <u>iletisim@teknofest.org</u> e-mail address.

It is important that your technical and organizational questions are conveyed through the correct channels above, in order to be able to respond quickly to the questions asked.

# **4 TECHNICAL RULES**

## 4.1 Design Environment and Technology

In the digital processor design category, Verilog-2005 or System Verilog hardware design language (HDL) must be used for the hardware to be developed. The rules given in section APP-3 must be followed while writing the HDL code. The design must be updated at least once in 20-days periods to a private repository opened on GitHub and shared with the competition evaluation board. Design contents to be uploaded to Github will be determined by DDK. In the chip design phase, either OpenLane flow or commercial EDA tool (e.g. Synopsys, Cadence or Siemens) flow will be used. IC flow evaluations will be done at TT (Typical-Typical) – 25 C - 1.80V corner. Minimum operating frequency should be 100 MHz.

In the analog design category, commercial-grade EDA tools (vendors like Synopsys, Cadence, Siemens) and its appropriate PDK will be used. Version information for the PDK and the tools will be shared in a later announcement. The designs will be updated to a special repository created on GitHub before the delivery of the detail design report and final presentation and will be shared with the competition evaluation board.

In the microcontroller design category, for the hardware to be developed Verilog or SystemVerilog hardware design language (HDL) must be used. The design has been shared with the competition evaluation board and must be updated at least every 20 days in a special repository opened on GitHub. Design contents to be uploaded to Github will be determined by DDK. During the chip design phase, an open source (OpenLane) or commercial EDA tool (such as Synopsys, Cadence, Siemens) and PDK suitable for these tools will be used. Details will be shared by DDK at a later date. The UVM library and SystemVerilog HDL should be used for UART peripheral verification. When verifying the processor core defined in the specification that will be used in the SoC, the test programs should be shown to be working correctly by comparing them with the Spike ISS results.

GitHub repositories of the participating teams should be shared with the "TUTEL-TUBITAK" account for the digital processor design and analog design category, and with the "yongatek-teknofest" account for the microcontroller design category. Contestants are required to share their GitHub repositories with the relevant accounts from the date to be determined later. Otherwise, they will lose points as stated in the scoring section. The date from which the repository should begin to be shared will be announced later.

#### 4.2 Design Requirements

#### 4.2.1 Digital Processor Design Category

In the digital processor design category of the competition, a customized processor with the RV32IMAFB\_Zicsr Instruction Set Architecture is expected to be designed. During the processor design phase, the constraints specified in Design Environment and Technology section must be complied with. Participants can reuse circuits

available within the open-source design community (appropriate references should be provided).

The features that the processor in question should have are listed below.

- Support for the instructions given in APP-1

- Supporting UART peripheral detailed in APP-2.

- Total 4 KB level 1 cache (L1 Cache) for holding the instructions and the data.

- 128-bit off-chip interface in the processor design for data that is not in level 1 cache (Signals in the interface and the specifications of the transfers will be determined in the top module (wrapper) to be shared by the competition committee.)

- This interface should be used for data from the end address of the peripherals to the end address of the main memory, and data outside the main memory region should be forwarded to the processor without storing into caches

- Only the main memory area, which starts from the address 0x80000000, should be cachable.

- The program counter value at boot time should point to the base address of the main memory

# 4.2.2 Analog Design Category

Today, the trend towards portable devices requires that many electronic systems be designed to operate with batteries. Power management circuits designed in this direction are implemented in integrated circuits instead of discrete elements in order to meet increased performance, low power consumption and space demand.

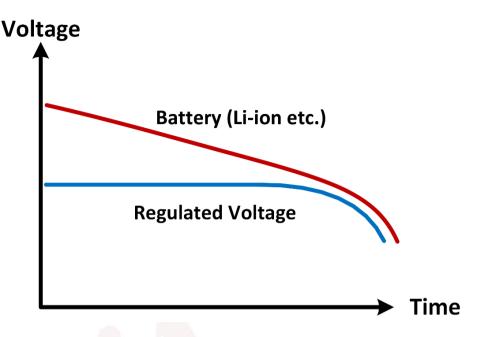

Figure 1 shows a representative time-voltage graph of a battery. Some batteries discharge almost linearly while powering the circuit due to their characteristic. When the circuits are fed directly with the battery, the performance of the circuit also changes over time as a result of the time-varying supply voltage and deviates from the optimum performance. In order to avoid this problem, power converters are used to convert the battery voltage to a constant voltage and provide it to the circuit.

Figure 1: Battery Discharge Graph

LDO (Low-Dropout) voltage regulator circuit is one of the commonly used power converter types to obtain a constant and noiseless voltage in battery powered systems. It is preferred because of its simpler structure and more affordable cost compared to other converter types. It is frequently used in battery powered systems such as automotive, mobile phones and laptop computers. The operation of this circuit is that it gives the variable or noise voltage at the input as a constant voltage at the output.

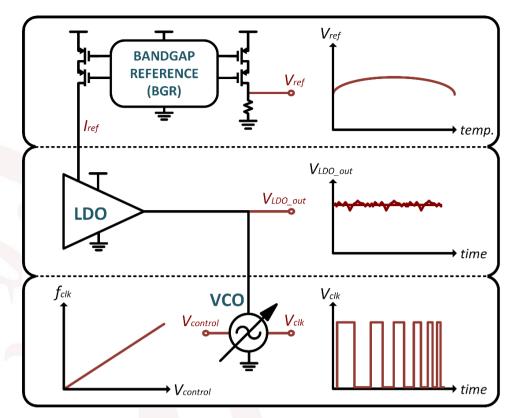

Designers are requested to design an LDO (Low-Dropout) voltage regulator and a voltage-controlled oscillator (VCO) to be powered by this regulator. VCO will have technical requirements that can be used in L1 and L2 GPS systems. It is also expected that the bandgap reference circuit will be designed to generate the reference voltage of the LDO voltage regulator. In Figure 2, the blocks to be designed within the scope of the competition are visualized.

Figure 2: Block Diagram of Bandgap Reference, LDO Voltage Regulator and Voltage Controlled Oscillator Circuits

Block level and general design requirements are given below in detail.

#### **General Requirements:**

- The design environment and technology specified in Section 3.1 must be complied with.

- The band-gap reference and LDO voltage regulator circuits should be powered by only one ideal voltage source of 1.8 V.

- All circuit elements should be used from the process library, ideal elements should not be used.

- Simulations should be made at the TT (Typical-Typical) process corner and at 27°C. The 27°C temperature is the nominal temperature at which the entire design will operate. Only simulations of the bandgap reference voltage circuit should cover the temperature range of -40°C to 125°C.

- Verify that the following requirements are met by post-layout simulations.

- The schematic and post-layout simulation results should be presented comparatively.

- Except for start-up circuits, all MOS transistors must operate in the saturation region. (Applicable to bandgap reference and LDO voltage regulator circuits)

- Stability analysis should be performed when necessary.

#### LDO regulator requirements:

• Input voltage should be 1.8V, output voltage should be 1.2V.

- The output voltage should show a maximum variation of 300 mV against current pulses with a pulse-period ratio of 50% from 0 mA to 50 mA. (The current pulse frequency must be 500 kHz and the current pulse source must be connected so that current flow from the regulator output to ground.)

- Loop gain and loop phase margin values should be minimum 45 dB and 50°.

- The above requirements should be tested by connecting an ideal 500 pF capacitor to the output. This capacitor is for the test setup and should not be included in the circuit.

- If there is no load at its output, the power consumption of the LDO voltage regulator should be a maximum of 1.8 mW.

- Line regulation should be checked by making the input voltage 2.5V.

- Load regulation should be checked by drawing a constant 10mA and 20mA current from the output.

#### Voltage-controlled oscillator (VCO) requirements:

- The VCO must be powered by the LDO voltage regulator and the supply voltage must be 1.2V.

- A decoupling capacitor can be connected to the VCO supply input. (It should be in VCO layout if it's connected.)

- The load to be driven at the VCO output must be at least 0.4pF. This capacitance should only be connected in the test schematic. It shouldn't be in the VCO block. Therefore, it doesn't need to be in the VCO layout.

- The VCO must be able to drive this load in a square wave form between 0 and 1.2V (rail-to-rail)

- VCO operating frequency should be between 1200 1600 MHz.

- Kvco value shouldn't be greater than 800 MHz/V.

- Phase Noise value must be better than 75 dBc for 1 MHz offset.

- The VCO control voltage range should be in the range of 0 1.2 V.

- The duty cycle value for the square wave obtained while driving the VCO load should be between 40%-60%.

- The sum of "rise time" + "fall time" for the square wave obtained while driving a load of 0.4pF at 1600MHz frequency should be less than 0.2ns. (For the rise time, should be looked at the time when the amplitude of the square wave increases from 10% to 90%. For the fall time, should be looked at the time when the amplitude of the square wave decreases from 90% to 10%.)

#### Bandgap reference voltage circuit requirements:

- A 500 mV reference voltage should be generated as shown in Figure 2 for the purpose of validating the bandgap reference circuit.

- The reference voltage should vary by a maximum of 20 ppm/°C, covering the temperature range of -40°C to 125°C.

- For 1.8±10% supply voltage, the 500mV reference voltage should not change and the transistors should protect their nominal operating regions.

- A start-up circuit should be utilized to avoid circuit startup problems.

- The PSRR value should be below 0 dB in the 1 Hz-10 GHz range.

## 4.2.3 Microcontroller Design Category

Two solutions will be realized under the microcontroller category: The first will work on FPGA (FPGA prototyping), the second will be to create production files with the physical design tool (IC Design).

The microcontroller to be designed by the competitors will use the CV32E40P RISC-V core IP with a single-core, 32-bit 4-stage pipeline, which is maintained by the "OpenHW Group" and available as open source in the github environment. The github repo link of the relevant processor core is given below:

https://github.com/openhwgroup/cv32e40p

The documentation link for the CV32E40P processor core is given below:

https://docs.openhwgroup.org/projects/cv32e40p-user-manual/en/latest/index.html

Which release and commit version and which configuration of the IP will be used within the scope of the competition, that is, which commands it will support or not, will be clarified by DDK at a later date.

The microcontroller will have the following peripherals:

1x UART

1x I2C Master

1x QSPI Master

1x Timer

1x GPIO (32 pin I/O)

1x USB Full-Speed Device (12 Mbps)

1x JTAG (Optional)

Register definitions and other details regarding peripheral units are defined under the heading "APP-4 Microcontroller Peripheral Registers".

Competitors can design peripheral designs themselves, or they can use open-source projects by referencing them.

The following open-source repos are provided by DDK as examples for USB Device peripheral design:

https://github.com/WangXuan95/FPGA-USB-Device

https://github.com/ulixxe/usb\_cdc

In USB Device design, competitors are expected to realize USB Communication Device Class (USB-CDC) functionality. Other device class functions (audio, HID, mass storage, video, etc.) will be optional and will provide additional points. Validation of the CV32E40P RISC-V processor core is expected to be done with an instruction set emulator (ISP) (e.g. Spike ISS). Spike ISS github repo link:

#### https://github.com/riscv-software-src/riscv-isa-sim

As part of microcontroller verification, the UART peripheral will be expected to be done using SystemVerilog HDL and Universal Verification Methodology (UVM). In the verification made with UVM, regression and coverage results must be reported. The environment in which UVM will be used (Synopsys, Cadence, Mentor) will be clarified by DDK at a later date.

It is not necessary to use UVM/SV for other peripherals other than UART. Verification can also be performed with other methods and methodologies. However, all peripherals and the MCU top module must be verified.

MCU will contain 8 kB instruction and 8 kB data memory.

Addressing of peripherals and memories will be defined and designed by the competitors.

When the system is powered on, it will boot from a non-volatile memory (QSPI Flash Memory) via the QSPI master interface. The bootloader code will be located in a small ROM (e.g. 512 Bytes or 1 kB) as a piece of code that cannot be changed. When the system is powered on, the Bootloader code will be run first. This piece of code will read the program to be run from Flash memory via the QSPI Master interface and write it to the instruction memory. Afterwards, it will transfer the execution to the instruction memory.

Optionally, a debug module connected to the JTAG interface will be designed. The debug module will be connected to the "debug" port of the CV32E40P processor core and the program running on the MUC can be debugged through this debug module.

# 4.3 Design Outputs

**Digital processor design category:** The expected design outputs are listed below. All these outputs can be generated via standard OpenLane flow. The files given below must be reproducible through the design in the repository created by the competitors on GitHub.

- GDSII (.gds): The industry standard layout file format used for submitting the design to manufacturing. DRC (Design Rule Check) will be performed by reading GDSII (Graphic Design System) via EDA tool. LVS (Layout versus Schematic) will also be done using this file format.

- Gate level netlist after layout (.v): The gate level netlist shows the standard cells and their connections in the design obtained after the chip flow. By using the gate level during the simulation, it will be verified that the design gives the correct outputs against the given inputs even after the chip flow.

- SDF (Standard Delay Format): SDF refers to the delay information of standard cells and the connections between them.

- DEF (.def): The DEF (Design Exchange Format) file contains the location of standard cells in addition to the port level netlist. By reading over the relevant EDA tool, general examinations about the design will be made and field information will be obtained.

- Reports: The design needs to be clean in terms of timing (setup, hold), DRV (maximum capacitance, max slew), and physical verification (DRC, LVS). For this purpose, test/analysis reports should be given.

Gate level simulation will not be counted among the minimum performance criteria, but it will have a point equivalent in the evaluation. For this reason, the relevant file must be submitted.

The expected design outputs for **analog design category** are as follows:

- GDSII (.gds) (GDS: Graphic Design System): The industry standard layout file format used for submitting the design to production. It will be used for layout evaluation and physical verifications (DRC/LVS).

- Design and test environment schematics: These are the files created by EDA tool Schematic Editor that contain the transistor-level designs and the test environment related to these designs. All schematic files used in the project should be included in the printouts to validate my designs.

- Schematic and post-layout transistor level netlist (.spice/.scs/.l): The transistor level netlist is the file showing the PDK elements in the design and their connections with each other. In the post-deployment netlist, parasitic elements are also included in this file. This file will be used for pre- and post-layout performance verifications.

- Layout output files: EDA tool Layout Editor output file. It is requested for the control of the layout.

- Physical Verification Reports: It consists of reports containing the results of physical verification tests (DRC/LVS).

Teams are required to upload their work to a remote repository or server location determined by DDK by a date to be specified later. Announcement about the upload format will be shared with the teams.

For the **microcontroller design category**, different outputs are expected for FPGA and physical design flows. The outputs are expected to be in the GitHub account, which the teams will share with the microcontroller design category regulatory company.

Different outputs are expected for the FPGA and physical design flow for the **microcontroller design category**. The outputs are expected to be in the GitHub account that the teams will share with the DDK.

**FPGA** Flow

- All RTL Verilog/SV design codes

- All testbench Verilog/SV codes

- Successful (error free) synthesis result report

- Successful (error free) stating timing analysis report

- Successful (error free) implementation (Place & Route) result report

- Bitstream that can be loaded into the FPGA

IC Physical Design Flow

- All RTL Verilog/SV design codes

- All testbench Verilog/SV codes

- Successful completion of physical design flow

- Production ready LEF, DEF, GDSII file outputs of the design

- Successful completion of physical design signoff tests (LVS, DRC, ERC, etc.)

# 5 AWARD

As a result of the evaluation, the teams that pass the report stages and reach the finals in their own category, meet the award criteria and are ranked in the final evaluation, will be awarded a monetary award as indicated in Table 2, Table 3 and Table 4. Categories will be evaluated and awarded separately. First, second and third place prizes will be divided equally according to the total number of team members (all members registered in the system) and will be deposited into the bank account specified by each person. The relevant category organizer will determine whether the teams that cannot meet the minimum success criteria for the award ranking in the competition categories can receive an honorable mention award or how much they can receive.

The prizes in the table below show the total amount that will be awarded to the teams that are eligible to receive the prize, no individual prizes will be awarded. The first, second and third prizes will be divided equally according to the total number of team members (excluding the consultant) and will be deposited into the bank account specified by each person. Team consultants who are entitled to receive an award cannot benefit from the first, second and third prize amounts below, the awards to be given to the consultants are also stated in the table below.

| RANK   | AWARD AMOUNT | CONSULTANT |

|--------|--------------|------------|

| First  | 150.000,00 も | 9.000,00 も |

| Second | 120.000,00 も | 7.500,00 も |

| Third  | 100.000,00 も | 6.000,00 も |

#### Table 2: Digital Processor Category Awards

#### Table 3: Analog Category Awards

| RANK   | AWARD AMOUNT | CONSULTANT |

|--------|--------------|------------|

| First  | 150.000,00 も | 9.000,00 も |

| Second | 120.000,00 も | 7.500,00 も |

| Third  | 100.000,00 も | 6.000,00 も |

Table 4: Microcontroller Category Awards

| RANK   | AWARD AMOUNT | CONSULTANT |

|--------|--------------|------------|

| First  | 150.000,00 も | 9.000,00 も |

| Second | 120.000,00 も | 7.500,00 も |

| Third  | 100.000,00 も | 6.000,00 も |

# 5.1 Minimum Success Criteria for Award Ranking in Digital Processor Design Category

The minimum success criteria that competitors must meet in order to enter the award ranking are as follows:

- The processor must support all 32-bit instructions given in this document.

- The processor must meet the requirements given in Digital Processor Design Category section that is below the Design Requirements header.

- The checks specified in the Design Outputs section, should be performed to show that there are no violations.

- The processor must successfully run test software prepared in line with the requirements.

In addition, the competitor must have passed to the presentation stage and must be in the festival area on the day of the event.

# 5.2 Minimum Success Criteria for Award Ranking in Analog Design Category

Competitors must meet following specifications at post-layout simulations in order to enter the award ranking:

- Functional operation of the all circuits must be correct.

- LDO loop gain and loop phase margin

- VCO operating frequency and pulse-period ratio

- The temperature coefficient and PSRR value of the band gap reference circuit

Also, the competitors must have passed the presentation stage and be present in the festival area on the day of the event.

# 5.3 Minimum Success Criteria for Award Ranking in Microcontroller Design Category

The minimum success criteria required for the contestants to be eligible for an award are given below.

- Demonstration that the microcontroller successfully carries out the test scenarios given by the DDK on the FPGA development board.

- Verifying the UART peripheral in the microcontroller with UVM/SV and creating regression and coverage test reports in this context.

- Preparing GDSII outputs ready for production by successfully completing the physical design flow.

# **6 GENERAL RULES**

<u>Click here</u> to access the General Rules booklet which is valid for the competition.

# **7 CODES OF CONDUCT**

<u>Click here</u> to access the Code of Ethics booklet that is valid for the competition.

## **Responsibility Statement**

• T3 Foundation and TEKNOFEST are not responsible for any product delivered by the competitors or any injury or damage caused by the competitor. T3 Foundation and organization officials are not responsible for the damages caused by the competitors to third parties. T3 Foundation and TEKNOFEST are not responsible for ensuring that the teams prepare and implement their systems within the framework of the laws of the Republic of Turkiye.

Turkiye Technology Team Foundation reserves the right to make any changes in this specification.

# 8 APPENDIX

# APP-1 Instructions to Be Supported

|              | imm[31:12]     |     |         | rd          | 0110111 | LUI   |

|--------------|----------------|-----|---------|-------------|---------|-------|

|              | imm[31:12]     | rd  | 0010111 | AUIPC       |         |       |

| im           | m[20 10:1 11 1 | rd  | 1101111 | JAL         |         |       |

| imm[11:      | 0]             | rs1 | 000     | rd          | 1100111 | JALR  |

| imm[12 10:5] | rs2            | rs1 | 000     | imm[4:1 11] | 1100011 | BEQ   |

| imm[12 10:5] | rs2            | rs1 | 001     | imm[4:1 11] | 1100011 | BNE   |

| imm[12 10:5] | rs2            | rs1 | 100     | imm[4:1 11] | 1100011 | BLT   |

| imm[12 10:5] | rs2            | rs1 | 101     | imm[4:1 11] | 1100011 | BGE   |

| imm[12 10:5] | rs2            | rs1 | 110     | imm[4:1 11] | 1100011 | BLTU  |

| imm[12 10:5] | rs2            | rs1 | 111     | imm[4:1 11] | 1100011 | BGEU  |

| imm[11:      | 1              | rs1 | 000     | rd          | 0000011 | LB    |

| imm[11:      | 0]             | rs1 | 001     | rd          | 0000011 | LH    |

| imm[11:      | 0]             | rs1 | 010     | rd          | 0000011 | LW    |

| imm[11:      | 1              | rs1 | 100     | rd          | 0000011 | LBU   |

| imm[11:      | 0]             | rs1 | 101     | rd          | 0000011 | LHU   |

| imm[11:5]    | rs2            | rs1 | 000     | imm[4:0]    | 0100011 | SB    |

| imm[11:5]    | rs2            | rs1 | 001     | imm[4:0]    | 0100011 | SH    |

| imm[11:5]    | rs2            | rs1 | 010     | imm[4:0]    | 0100011 | SW    |

| imm[11:      |                | rs1 | 000     | rd          | 0010011 | ADDI  |

| imm[11:      | 0]             | rs1 | 010     | rd          | 0010011 | SLTI  |

| imm[11:      | 1              | rs1 | 011     | rd          | 0010011 | SLTIU |

| imm[11:      | 1              | rs1 | 100     | rd          | 0010011 | XORI  |

| imm[11:      | 1              | rs1 | 110     | rd          | 0010011 | ORI   |

| imm[11:      | 1              | rs1 | 111     | rd          | 0010011 | ANDI  |

| 0000000      | shamt          | rs1 | 001     | rd          | 0010011 | SLLI  |

| 0000000      | shamt          | rs1 | 101     | rd          | 0010011 | SRLI  |

| 0100000      | shamt          | rs1 | 101     | rd          | 0010011 | SRAI  |

| 0000000      | rs2            | rs1 | 000     | rd          | 0110011 | ADD   |

| 0100000      | rs2            | rs1 | 000     | rd          | 0110011 | SUB   |

| 0000000      | rs2            | rs1 | 001     | rd          | 0110011 | SLL   |

| 0000000      | rs2            | rs1 | 010     | rd          | 0110011 | SLT   |

| 0000000      | rs2            | rs1 | 011     | rd          | 0110011 | SLTU  |

| 0000000      | rs2            | rs1 | 100     | rd          | 0110011 | XOR   |

| 0000000      | rs2            | rs1 | 101     | rd          | 0110011 | SRL   |

| 0100000      | rs2            | rs1 | 101     | rd          | 0110011 | SRA   |

| 0000000      | rs2            | rs1 | 110     | rd          | 0110011 | OR    |

| 0000000      | rs2            | rs1 | 111     | rd          | 0110011 | AND   |

Table 5 : RV32I Basic Instruction Set

Table 6: RV32M Standard Instruction Set Extensions

| 0000001 | rs2 | rs1 | 000 | rd | 0110011 | MUL    |

|---------|-----|-----|-----|----|---------|--------|

| 0000001 | rs2 | rs1 | 001 | rd | 0110011 | MULH   |

| 0000001 | rs2 | rs1 | 010 | rd | 0110011 | MULHSU |

| 0000001 | rs2 | rs1 | 011 | rd | 0110011 | MULHU  |

| 0000001 | rs2 | rs1 | 100 | rd | 0110011 | DIV    |

| 0000001 | rs2 | rs1 | 101 | rd | 0110011 | DIVU   |

| 0000001 | rs2 | rs1 | 110 | rd | 0110011 | REM    |

| 0000001 | rs2 | rs1 | 111 | rd | 0110011 | REMU   |

## Table 7: RV32A Standard Instruction Set Extensions

| 00010 | 0.0 | rl | 00000 |     | 010 |    | 0101111 | LR.W      |

|-------|-----|----|-------|-----|-----|----|---------|-----------|

| 00010 | aq  | rı | 00000 | rs1 | 010 | rd | 0101111 | LR.W      |

| 00011 | aq  | rl | rs2   | rs1 | 010 | rd | 0101111 | SC.W      |

| 00001 | aq  | rl | rs2   | rs1 | 010 | rd | 0101111 | AMOSWAP.W |

| 00000 | aq  | rl | rs2   | rs1 | 010 | rd | 0101111 | AMOADD.W  |

| 00100 | aq  | rl | rs2   | rs1 | 010 | rd | 0101111 | AMOXOR.W  |

| 01100 | aq  | rl | rs2   | rs1 | 010 | rd | 0101111 | AMOAND.W  |

| 01000 | aq  | rl | rs2   | rs1 | 010 | rd | 0101111 | AMOOR.W   |

| 10000 | aq  | rl | rs2   | rs1 | 010 | rd | 0101111 | AMOMIN.W  |

| 10100 | aq  | rl | rs2   | rs1 | 010 | rd | 0101111 | AMOMAX.W  |

| 11000 | aq  | rl | rs2   | rs1 | 010 | rd | 0101111 | AMOMINU.W |

| 11100 | aq  | rl | rs2   | rs1 | 010 | rd | 0101111 | AMOMAXU.W |

#### Table 8: RV32F Standard Instruction Set Extensions

| RV32F Standard Extension |           |       |     |               |          |         |           |  |

|--------------------------|-----------|-------|-----|---------------|----------|---------|-----------|--|

|                          | imm[11:0] |       | rs1 | 010           | rd       | 0000111 | FLW       |  |

| imm[11                   | .:5]      | rs2   | rs1 | 010           | imm[4:0] | 0100111 | FSW       |  |

| rs3                      | 00        | rs2   | rs1 | rm            | rd       | 1000011 | FMADD.S   |  |

| rs3                      | 00        | rs2   | rs1 | rm            | rd       | 1000111 | FMSUB.S   |  |

| rs3                      | 00        | rs2   | rs1 | rm            | rd       | 1001011 | FNMSUB.S  |  |

| rs3                      | 00        | rs2   | rs1 | rm            | rd       | 1001111 | FNMADD.S  |  |

| 00000                    | 00        | rs2   | rs1 | rm            | rd       | 1010011 | FADD.S    |  |

| 000010                   | 00        | rs2   | rs1 | rm            | rd       | 1010011 | FSUB.S    |  |

| 000100                   | 00        | rs2   | rs1 | rm            | rd       | 1010011 | FMUL.S    |  |

| 000110                   | 00        | rs2   | rs1 | rm            | rd       | 1010011 | FDIV.S    |  |

| 010110                   | 00        | 00000 | rs1 | rm            | rd       | 1010011 | FSQRT.S   |  |

| 001000                   | 00        | rs2   | rs1 | 000           | rd       | 1010011 | FSGNJ.S   |  |

| 001000                   | 00        | rs2   | rs1 | 001           | rd       | 1010011 | FSGNJN.S  |  |

| 001000                   | 00        | rs2   | rs1 | 010           | rd       | 1010011 | FSGNJX.S  |  |

| 001010                   | 00        | rs2   | rs1 | 000           | rd       | 1010011 | FMIN.S    |  |

| 001010                   | 00        | rs2   | rs1 | 001           | rd       | 1010011 | FMAX.S    |  |

| 110000                   | 00        | 00000 | rs1 | $\mathbf{rm}$ | rd       | 1010011 | FCVT.W.S  |  |

| 110000                   | 00        | 00001 | rs1 | rm            | rd       | 1010011 | FCVT.WU.S |  |

| 11100                    | 00        | 00000 | rs1 | 000           | rd       | 1010011 | FMV.X.W   |  |

| 101000                   | 00        | rs2   | rs1 | 010           | rd       | 1010011 | FEQ.S     |  |

| 101000                   | 00        | rs2   | rs1 | 001           | rd       | 1010011 | FLT.S     |  |

| 101000                   | 00        | rs2   | rs1 | 000           | rd       | 1010011 | FLE.S     |  |

| 11100                    | 00        | 00000 | rs1 | 001           | rd       | 1010011 | FCLASS.S  |  |

| 110100                   | 00        | 00000 | rs1 | rm            | rd       | 1010011 | FCVT.S.W  |  |

| 110100                   | 00        | 00001 | rs1 | $\mathbf{rm}$ | rd       | 1010011 | FCVT.S.WU |  |

| 111100                   | 00        | 00000 | rs1 | 000           | rd       | 1010011 | FMV.W.X   |  |

#### RV32F Standard Extension

#### Table 9: RV32B Standard Instruction Set Extensions

The designed processor must support the instructions where RV32 is marked in the table.

| RV32                  | <b>RV64</b>                                                                  | Mnemonic                                                                                                                                                                                                | Instruction                                                                                                                                                                                                                                                                                                  | Zba                            | Zbb                            | Zbc | Zbs |

|-----------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|-----|-----|

|                       | $\checkmark$                                                                 | add.uw rd, rs1, rs2                                                                                                                                                                                     | Add unsigned word                                                                                                                                                                                                                                                                                            | $\checkmark$                   |                                |     |     |

| ~                     | ~                                                                            | andn rd, rs1, rs2                                                                                                                                                                                       | AND with inverted operand                                                                                                                                                                                                                                                                                    |                                | ~                              |     |     |

| <                     | $\checkmark$                                                                 | clmul rd, rs1, rs2                                                                                                                                                                                      | Carry-less multiply (low-part)                                                                                                                                                                                                                                                                               |                                |                                | ~   |     |

| ~                     | ~                                                                            | clmulh rd, rs1, rs2                                                                                                                                                                                     | Carry-less multiply (high-part)                                                                                                                                                                                                                                                                              |                                |                                | ~   |     |

| $\checkmark$          | ~                                                                            | clmulr rd, rs1, rs2                                                                                                                                                                                     | Carry-less multiply (reversed)                                                                                                                                                                                                                                                                               |                                |                                | ~   |     |

| ~                     | ~                                                                            | clz rd, rs                                                                                                                                                                                              | Count leading zero bits                                                                                                                                                                                                                                                                                      |                                | ~                              |     |     |

|                       | ~                                                                            | clzw rd, rs                                                                                                                                                                                             | Count leading zero bits in word                                                                                                                                                                                                                                                                              |                                | ~                              |     |     |

| $\checkmark$          | ~                                                                            | cpop rd, rs                                                                                                                                                                                             | Count set bits                                                                                                                                                                                                                                                                                               |                                | ~                              |     |     |

|                       | ~                                                                            | cpopw rd, rs                                                                                                                                                                                            | Count set bits in word                                                                                                                                                                                                                                                                                       |                                | ~                              |     |     |

| ~                     | ~                                                                            | ctz rd, rs                                                                                                                                                                                              | Count trailing zero bits                                                                                                                                                                                                                                                                                     |                                | V                              |     |     |

|                       | ~                                                                            | ctzw rd, rs                                                                                                                                                                                             | Count trailing zero bits in word                                                                                                                                                                                                                                                                             |                                | ~                              |     |     |

| <i>v</i>              | ~                                                                            | max rd, rs1, rs2                                                                                                                                                                                        | Maximum                                                                                                                                                                                                                                                                                                      |                                | ~                              |     |     |

| ~                     | ~                                                                            | maxu rd, rs1, rs2                                                                                                                                                                                       | Unsigned maximum                                                                                                                                                                                                                                                                                             |                                | ~                              |     |     |

| ~                     | ~                                                                            | min rd, rs1, rs2                                                                                                                                                                                        | Minimum                                                                                                                                                                                                                                                                                                      |                                | ~                              |     |     |

| ~                     | ~                                                                            | minu rd, rs1, rs2                                                                                                                                                                                       | Unsigned minimum                                                                                                                                                                                                                                                                                             |                                | ~                              |     |     |

| ~                     | ~                                                                            | orc.b rd, rs1, rs2                                                                                                                                                                                      | Bitwise OR-Combine, byte granule                                                                                                                                                                                                                                                                             |                                | ~                              |     |     |

| ~                     | ~                                                                            | orn rd, rs1, rs2                                                                                                                                                                                        | OR with inverted operand                                                                                                                                                                                                                                                                                     |                                | ~                              |     |     |

| $\checkmark$          | ~                                                                            | rev8 rd, rs                                                                                                                                                                                             | Byte-reverse register                                                                                                                                                                                                                                                                                        |                                | ~                              |     |     |

| ~                     | ~                                                                            | rol rd, rs1, rs2                                                                                                                                                                                        | Rotate left (Register)                                                                                                                                                                                                                                                                                       |                                | ~                              |     |     |

|                       | ~                                                                            | rolw rd, rs1, rs2                                                                                                                                                                                       | Rotate Left Word (Register)                                                                                                                                                                                                                                                                                  | - 10                           | V                              |     |     |

| ~                     | ~                                                                            | ror rd, rs1, rs2                                                                                                                                                                                        | Rotate right (Register)                                                                                                                                                                                                                                                                                      |                                | ~                              |     |     |

| ~                     | ~                                                                            | rori rd, rs1, shamt                                                                                                                                                                                     | Rotate right (Immediate)                                                                                                                                                                                                                                                                                     |                                | ~                              |     |     |

|                       | ~                                                                            | roriw rd, rs1, shamt                                                                                                                                                                                    | Rotate right Word (Immediate)                                                                                                                                                                                                                                                                                |                                | V                              |     |     |

|                       | ~                                                                            | rorw rd, rs1, rs2                                                                                                                                                                                       | Rotate right Word (Register)                                                                                                                                                                                                                                                                                 |                                | ~                              |     |     |

| RV32                  | RV64                                                                         | Mnemonic                                                                                                                                                                                                | Instruction                                                                                                                                                                                                                                                                                                  | Zba                            | Zbb                            | Zbc | Zbs |

| ~                     | ~                                                                            | bclr rd, rs1, rs2                                                                                                                                                                                       | Single-Bit Clear (Register)                                                                                                                                                                                                                                                                                  |                                |                                |     | ~   |

| ~                     | ~                                                                            | bclri rd, rs1, imm                                                                                                                                                                                      | Single-Bit Clear (Immediate)                                                                                                                                                                                                                                                                                 |                                |                                |     | ~   |

| ~                     | ~                                                                            | bext rd, rs1, rs2                                                                                                                                                                                       | Single-Bit Extract (Register)                                                                                                                                                                                                                                                                                |                                |                                |     | ~   |

| ~                     | ~                                                                            | bexti rd, rs1, imm                                                                                                                                                                                      | Single-Bit Extract (Immediate)                                                                                                                                                                                                                                                                               |                                |                                |     | ~   |

| ~                     | ~                                                                            | binv rd, rs1, rs2                                                                                                                                                                                       | Single-Bit Invert (Register)                                                                                                                                                                                                                                                                                 |                                |                                |     | ~   |

| $\checkmark$          | ~                                                                            | binvi rd, rs1, imm                                                                                                                                                                                      | Single-Bit Invert (Immediate)                                                                                                                                                                                                                                                                                |                                |                                |     | ~   |